TSMC debuts 1.6-nanometer process with new power distribution technology – Business

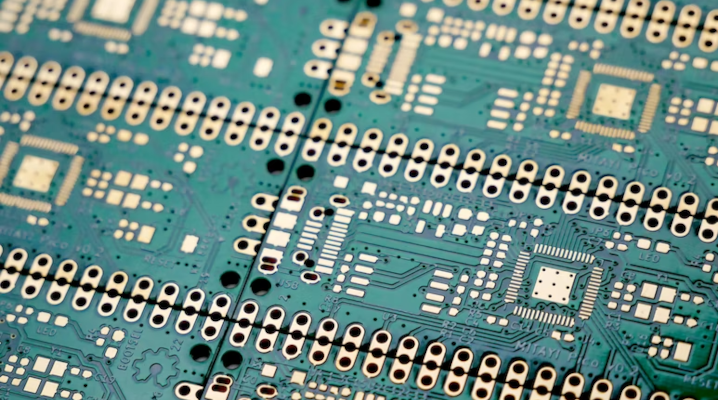

Taiwan Semiconductor Manufacturing Co. Ltd. has previewed a new chipmaking process that will facilitate the production of faster, more efficient data center processors.

TSMC’s 1.6-nanometer process, as the technology is known, made its debut today at a company event in Santa Clara, California. Executives also detailed a second upcoming chipmaking technology dubbed NanoFlex. It will allow customers to mix and match different types of transistors in the same processor.

In a modern chip, the transistors sit below a network of tiny wires that performs three tasks. The wires transport electricity to the transistors and move data between them to facilitate calculations. Additionally, they transmit the clock signal, a kind of cue that the processor emits at fixed time intervals to keep its circuits synced with one another.

TSMC’s 1.6-nanometer node takes a different approach to chip wiring. In processors made using the technology, the wires used to carry electricity to transistors will be located beneath those transistors rather than above them. This arrangement, which is known as backside power delivery, facilitates the production of more efficient chips.

One way the technology optimizes processors is by mitigating a technical issue known as IR drop. This phenomenon lowers the voltage of the electricity that a chip’s transistors receive, which slows their performance. TSMC says that the wires in its 1.6-nanometer node are less prone to such voltages drops.

Rival Intel Corp. is likewise implementing backside power delivery in its 20A process, which is also known as the company’s five-nanometer node. According to the company, its implementation of the technology not only streamlines electricity distribution but also allows a chip’s circuits to be packed closer together. The result is that more transistors can be placed on a processor to boost its computing capacity.

A transistor comprises four main components: the source, drain, channel and gate. The source is the entry point through which electricity flows into the transistor while the drain is the exit. The channel and gate, in turn, are responsible for orchestrating the movement of electrons.

The power delivery wires in TSMC’s 1.6-nanometer process connect directly to the source and drain. According to the company, that architecture is more complicated to manufacture than other backside power delivery implementations such as the one used by Intel. TSMC says that its decision to adopt a more complex design will help boost the efficiency of customers’ chips.

The company estimates that chips made using its 1.6-nanometer process will require 15% to 20% less electricity than previous-generation silicon. Alternatively, customers can trade off some power efficiency for increased performance. TSMC says a 1.6-nanometer chip can achieve up to 10% higher clock speeds than a previous-generation product using the same amount of energy.

At the event where the chipmaker debuted its 1.6-nanometer node, executives also detailed a second upcoming technology called NanoFlex. It provides the ability to create chips that combine multiple transistor types with different power-efficiency, speed and size configurations. That flexibility could enable customers to more closely align TSMC-made chips with their project requirements.

NanoFlex is set to debut with the company’s two-nanometer node, which is scheduled to enter mass production next year. The 1.6-nanometer process, in turn, is set to come online in the second half of 2026. Both nodes use TSMC’s gate-all-around transistor architecture.